Josephson junction count

The Josephson junction count is the number of Josephson junctions on a superconducting integrated circuit chip. Josephson junctions are active circuit elements in superconducting circuits. The Josephson junction count is a measure of circuit or device complexity, similar to the transistor count used for semiconductor integrated circuits.

Examples of circuits using Josephson junctions include digital circuits based on SFQ logic (e.g., RSFQ, RQL, adiabatic quantum flux parametron), superconducting quantum computing circuits, superconducting analog circuits, etc.

Integrated Circuits

The superconducting integrated circuits listed here must have been fabricated and tested, but are not required to be commercially available. Chip area includes the full extent of the chip.

| Reference | Description | Junction count |

Date | Maker | Process | Circuit [mm²] |

Chip [mm²] |

|---|---|---|---|---|---|---|---|

| [1] | RSFQ NOT gate | 13 | 1987 | Moscow State U. | 10 µm, 5 MA/m², 2 Nb | 1.1 | ? |

| CORE1α6[2] | RSFQ microprocessor, 8 bit | 6,319 | 2004 | NEC | 2 µm, 25 MA/m² | 10.9 | ? |

| SCRAM2[3] | RSFQ microprocessor, 8 bit | 8,197 | 2006 | SRL | 2 µm, 25 MA/m² | 15.3 | 25 |

| CORE1γ[4] | RSFQ microprocessor, 8 bit | 22,302 | 2007 | ISTEC | 2 µm, 25 MA/m² | 40.45 | 64 |

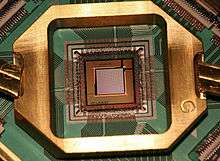

| Rainier[5] | RSFQ, 128 qubit QA processor | 23,360 | 2010 | D-Wave, SVTC | 250 nm, 2.5 MA/m²,[6] 6 Nb | 8 | 32 |

| Vesuvius | SFQ, 512 qubit QA processor | 96,000 | 2012 | D-Wave, SVTC | 250 nm, 2.5 MA/m², 6 Nb | 8 | 162 |

| [7] | RSFQ, 16-bit adder | 12,785 | 2012 | SBU, AIST | 1 µm, 100 MA/m², 10 Nb | 8.5 | 29.75 |

| [8] | 8,192 bit shift register | 32,800 | 2014 | SBU, MIT-LL | 500 nm, 100 MA/m², 8 Nb | 9 | 25 |

| Washington | SFQ, 2048 qubit QA processor | 128,472 | 2015 | D-Wave, Cypress | 250 nm, 2.5 MA/m², 6 Nb | 30 | 136 |

| [9] | RQL, 2 shift registers | 72,800 | 2015 | NGC, MIT-LL | 500 nm, 100 MA/m², 8 Nb | 9 | 25 |

Maker column may include organizations that designed and fabricated the chip.

Process column information: minimum linewidth, Josephson junction critical current density, superconducting layer number and materials. Conversions for units of critical current density: 1 MA/m2 = 1 µA/µm2 = 100 A/cm2.

Memory

Memory is an electronic data storage device, often used as computer memory, on a single integrated circuit chip. The superconducting integrated circuits listed here must have been fabricated and tested, but are not required to be commercially available. Chip area includes the full extent of the chip.

| Reference | Description | Junction count |

Date | Maker | Process | Circuit [mm²] |

Chip [mm²] |

|---|---|---|---|---|---|---|---|

| [10] | 1024 bit ROM, NbN/MgO/NbN junctions | 5,943 | 1990 | Electrotechnical Lab, Japan | 3 µm, 5.6 MA/m², 2 Nb + 1 Pb-In | 17.25 | |

| [11] | 4096 bit RAM | 23,488 | 2005 | ISTEC | 1 µm, 100 MA/m², 10 Nb | 5.5 | ? |

References

- ↑ Koshelets V, Likharev K, Migulin V, Mukhanov O, Ovsyannikov G, Semenov V, Serpuchenko I, Vystavkin A (1987). "Experimental realization of a resistive single flux quantum logic circuit". IEEE Trans. Magn. 23 (2): 755–758. doi:10.1109/TMAG.1987.1064953.

- ↑ Tanaka M, Kondo T, Nakajima N, Kawamoto T, Yamanashi Y, Kamiya Y, Akimoto A, Fujimaki A, Hayakawa H, Yoshikawa N, Terai H, Hashimoto Y, Yorozu S (2005). "Demonstration of a single-flux-quantum microprocessor using passive transmission lines". IEEE Trans. Appl. Supercond. 15 (2): 400–404. doi:10.1109/TASC.2005.849860.

- ↑ Nobumori Y, Nishigai T, Nakamiya K, Yoshikawa N, Fujimaki A, Terai H, Yorozu S (2007). "Design and Implementation of a Fully Asynchronous SFQ Microprocessor: SCRAM2". IEEE Trans. Appl. Supercond. 17 (2): 478–481. doi:10.1109/TASC.2007.898658.

- ↑ Tanaka M, Yamanashi Y, Irie N, Park H-J, Iwasaki S, Takagi K, Taketomi K, Fujimaki A, Yoshikawa N, Terai H, Yorozu S (2007). "Design and implementation of a pipelined 8 bit-serial single-flux-quantum microprocessor with cache memories". Supercond. Sci. Technol. 20 (11): S305–S309. doi:10.1088/0953-2048/20/11/S01.

- ↑ Johnson MW, Bunyk P, Maibaum F, Tolkacheva E, Berkley AJ, Chapple EM, Harris R, Johansson J, Lanting T, Perminov I, Ladizinsky E, Oh T, Rose G (2010). "A scalable control system for a superconducting adiabatic quantum optimization processor". Supercond. Sci. Technol. 23 (6): 065004. doi:10.1088/0953-2048/23/6/065004.

- ↑ Bunyk PI, Hoskinson EM, Johnson MW, Tolkacheva E, Altomare F, Berkley AJ, Harris R, Hilton JP, Lanting T, Przybysz AJ, Whittaker J (2014). "Architectural Considerations in the Design of a Superconducting Quantum Annealing Processor". IEEE Trans. Appl. Supercond. 24 (4): 1–10. doi:10.1109/TASC.2014.2318294.

- ↑ Dorojevets M, Ayala CL, Yoshikawa N, Fujimaki A (2010). "16-Bit Wave-Pipelined Sparse-Tree RSFQ Adder". IEEE Trans. Appl. Supercond. 23 (3): 1700605. doi:10.1109/TASC.2012.2233846.

- ↑ Semenov VK, Polyakov YA, Tolpygo SK (2015). "New AC-Powered SFQ Digital Circuits". IEEE Trans. Appl. Supercond. 25 (3): 1–7. doi:10.1109/TASC.2014.2382665.

- ↑ Herr QP, Osborne J, Stoutimore MJA, Hearne H, Selig R, Vogel J, Min E, Talanov VV, Herr AY (2015). "Reproducible operating margins on a 72 800-device digital superconducting chip". Supercond. Sci. Technol. 28: 124003. doi:10.1088/0953-2048/28/12/124003.

- ↑ Aoyagi M, Nakagawa H, Kurosawa I, Takada S (1991). "Josephson LSI fabrication technology using NbN/MgO/NbN tunnel junctions". IEEE Trans. Magn. 27 (2): 3180–3183. doi:10.1109/20.133887.

- ↑ Nagasawa S, Satoh T, Hinode K, Kitagawa Y, Hidaka M (2007). "Yield Evaluation of 10-kA/cm² Nb Multi-Layer Fabrication Process Using Conventional Superconducting RAMs". IEEE Trans. Appl. Supercond. 17 (2): 177–180. doi:10.1109/TASC.2007.898050.