Spin-transfer torque

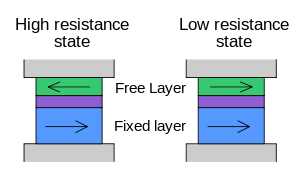

Spin-transfer torque is an effect in which the orientation of a magnetic layer in a magnetic tunnel junction or spin valve can be modified using a spin-polarized current.

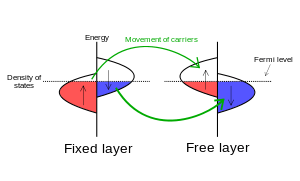

Charge carriers (such as electrons) have a property known as spin which is a small quantity of angular momentum intrinsic to the carrier. An electric current is generally unpolarized (consisting of 50% spin-up and 50% spin-down electrons); a spin polarized current is one with more electrons of either spin. By passing a current through a thick magnetic layer (usually called the “fixed layer”), one can produce a spin-polarized current. If this spin-polarized current is directed into a second, thinner magnetic layer (the “free layer”), angular momentum can be transferred to this layer, changing its orientation. This can be used to excite oscillations or even flip the orientation of the magnet. The effects are usually only seen in nanometer scale devices.

Spin-transfer torque memory

Spin-transfer torque can be used to flip the active elements in magnetic random-access memory. Spin-transfer torque magnetic random-access memory (STT-RAM or STT-MRAM) has the advantages of lower power consumption and better scalability over conventional magnetoresistive random-access memory (MRAM) which uses magnetic fields to flip the active elements. Spin-transfer torque technology has the potential to make possible MRAM devices combining low current requirements and reduced cost; however, the amount of current needed to reorient the magnetization is at present too high for most commercial applications, and the reduction of this current density alone is the basis for current academic research in spin electronics.[1]

Industrial development

Hynix Semiconductor and Grandis formed a partnership in April 2008 to explore commercial development of STT-RAM technology.[2][3]

Hitachi and Tohoku University demonstrated a 32-Mbit STT-RAM in June 2009.[4]

On August 1, 2011, Grandis announced that it had been purchased by Samsung Electronics for an undisclosed sum.[5]

In 2011, Qualcomm presented a 1 Mbit Embedded STT-MRAM, manufactured in TSMC's 45 nm LP technology at the Symposium on VLSI Circuits.[6]

In May 2011, Russian Nanotechnology Corp. announced an investment of $300 million in Crocus Nano Electronics (a joint venture with Crocus Technology) which will build an MRAM factory in Moscow, Russia.

In 2012 Everspin Technologies released the first commercially available DDR3 dual in-line memory module ST-MRAM which has a capacity of 64 Mb.[7]

Other companies working on STT-RAM include Avalanche Technology, Crocus Technology[8] and Spin Transfer Technologies.[9]

See also

References

- ↑ Ralph, D. C.; Stiles, M. D. (April 2008). "Spin transfer torques". Journal of Magnetism and Magnetic Materials. 320 (7): 1190–1216. arXiv:0711.4608

. doi:10.1016/j.jmmm.2007.12.019. ISSN 0304-8853. Retrieved 2009-05-22.

. doi:10.1016/j.jmmm.2007.12.019. ISSN 0304-8853. Retrieved 2009-05-22. - ↑ "Grandis press release describing partnership with Hynix" (PDF). Grandis. 2008-04-01. Archived from the original (PDF) on 2012-04-14. Retrieved 2008-08-15.

- ↑ "Hynix press release describing partnership with Grandis". Hynix. 2008-04-02. Retrieved 2008-08-15.

- ↑ "Session 8-4: 32-Mb 2T1R SPRAM with localized bi-directional write driver and '1'/'0' dual-array equalized reference cell". vlsisymposium.org. Archived from the original on 12 March 2012.

- ↑

- ↑ Kim, J.P.; Qualcomm Inc., San Diego, CA, USA; Taehyun Kim; Wuyang Hao; Rao, H.M.; Kangho Lee; Xiaochun Zhu; Xia Li; Wah Hsu; Kang, S.H.; Matt, N.; Yu, N. (15–17 June 2011). A 45nm 1Mb embedded STT-MRAM with design techniques to minimize read-disturbance. 2011 Symposium on VLSI Circuits (VLSIC),. ieeexplore.ieee.org. IEEE. ISBN 978-1-61284-175-5. ISSN 2158-5601.

- ↑ "Everspin ships first ST-MRAM memory with 500X performance of flash". Computerworld. 2012-11-12. Retrieved 2014-09-25.

- ↑ "Crocus press release describing MRAM new prototype". crocus-technology.com. Crocus. 2009-10-01. Archived from the original on 20 April 2012.

- ↑ "Interview with Vincent Chun from Spin Transfer Technologies". Mram-info.com. Retrieved 2014-02-07.

External links

- Spin torque applet

- J.C. Slonczewski:"Current-driven excitation of magnetic multilayers(1996)", Journal of Magnetism and Magnetic Materials Volume 159, Issues 1-2, June 1996, Pages L1-L7