TILE64

| Produced | 2007 |

|---|---|

| Common manufacturer(s) | |

| Max. CPU clock rate | 600 MHz to 900 MHz |

| Min. feature size | 45 nm to 90 nm |

| Cores | 64 |

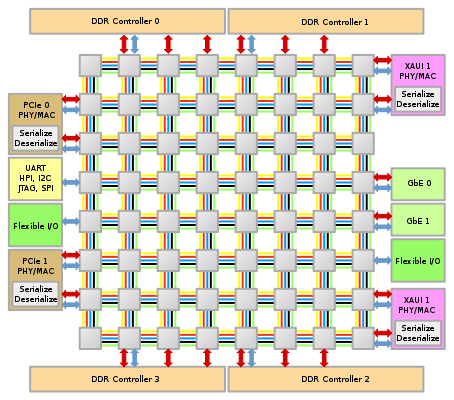

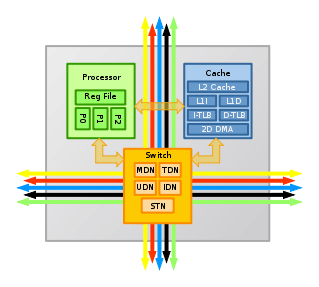

TILE64 is a multicore processor manufactured by Tilera. It consists of a mesh network of 64 "tiles", where each tile houses a general purpose processor, cache, and a non-blocking router, which the tile uses to communicate with the other tiles on the processor.

The short-pipeline, in-order, three-issue cores implement a MIPS-inspired[1] VLIW instruction set. Each core has a register file and three functional units: two integer arithmetic logic units and a load-store unit. Each of the cores ("tile") has its own L1 and L2 caches plus an overall virtual L3 cache which is an aggregate of all the L2 caches.[2] A core is able to run a full operating system on its own or multiple cores can be used to run a symmetrical multi-processing operating system.

TILE64 has four DDR2 controllers, two 10-gigabit Ethernet interfaces, two four-lane PCIe interfaces, and a "flexible" input/output interface, which can be software-configured to handle a number of protocols. The processor is fabricated using a 90 nm process and runs at speeds of 600 to 900 MHz.

|

|

According to CTO and co-founder Anant Agarwal, Tilera will target the chip at networking equipment and digital video markets where the demands for computing processing are high.[3]

Support for the TILE64 architecture was added to Linux kernel version 2.6.36.[4] Non-official LLVM back-end for Tilera exists.[5]

References

- ↑ https://stackoverflow.com/questions/6515358/what-instruction-set-is-used-by-tilera-microprocessors

- ↑ Kingman, Henry (August 20, 2007). "Massively multicore processor runs Linux". linuxdevices.com. Archived from the original on September 6, 2012.

- ↑ Boslet, Mark (August 20, 2007). "Start-up Tilera to Unveil 64-core chip". San Jose Mercury News.

- ↑ "Tilera architecture support". Kernel Newbies. October 20, 2010.

- ↑ Tilera TILE64 Back-End For LLVM Published // Phoronix, September 6, 2012

External links

- Tilera website

- MIT startup raises multicore bar with new 64-core CPU

- Chipmakers aim to unclog data paths at Archive.is (archived 2013-01-19)