PA-7100

The PA-7100 is a microprocessor developed by Hewlett-Packard (HP) that implemented the PA-RISC 1.1 instruction set architecture (ISA). It is also known as the PCX-T and by its code-name Thunderbird. It was introduced in early 1992 and was the first PA-RISC microprocessor to integrate the floating-point unit (FPU) on-die. It operated at 33 - 100 MHz and competed primarily with the Digital Equipment Corporation (DEC) Alpha 21064 in the workstation and server markets. PA-7100 users were HP in its HP 9000 workstations and Stratus Computer in its Continuum fault-tolerant servers.

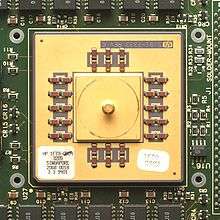

It was based on the PA-7000 (PCX-S) chip set, a previous PA-RISC implementation consisting of a microprocessor and FPU. The PA-7100 contains 850 000 transistors and measures 14.3 x 14.3 mm for an area of 204.49 mm². It was fabricated by HP in their CMOS26B process, a 0.8 µm complementary metal–oxide–semiconductor (CMOS) process. The PA-7100 is packaged in a 504-pin ceramic pin grid array that has a copper-tungsten heat spreader.

An improved PA-7100, the PA-7150 was introduced in 1994. It operated at 125 MHz, due to improved circuit design. It was fabricated in the same CMOS26B process as the PA-7100.

Both microprocessors were fabricated at HP's Corvallis, Oregon and Fort Collins, Colorado fabrication plants.[1]

The PA-7100LC and PA-7200 microprocessors were also based on the PA-7100.[2][3]

Notes

See also

- Amiga Hombre chipset (a Commodore-Amiga system which is based on PA-7150 CPU).

References

- PA-7100 PA-RISC Processor OpenPA.net

- Asprey, T. et al. (June 1993). "Performance features of the PA7100 microprocessor". IEEE Micro. pp. 22–35.

- Chan, Kenneth K. et al. (February 1996). "Design of the HP PA 7200 CPU". Hewlett-Packard Journal.

- DeLano, E. et al. (1992). "A high speed superscalar PA-RISC processor". Proceedings of Compcon. pp. 116–121.

- DeTar, Jim (20 December 1993). "HP spins PA-RISC architecture; part of five-year roadmap". Electronic News.

- Gwennap, Linley (7 March 1994). "PA-7200 Enables Inexpensive MP Systems". Microprocessor Report.

- Heikes, C. (1994). "A 4.5 mm2 multiplier array for a 200 MFLOP pipelined coprocessor". ISSCC Digest of Technical Papers. pp. 290–291.

- Yetter, J. et al. (1992). "A 100 MHz superscalar PA-RISC CPU/coprocessor chip". 1992 Symposium on VLSI Circuits. pp. 12–13.