Rock (processor)

| |

| Designed by | Sun Microsystems |

|---|---|

| Instruction set | SPARC V9 |

| Cores | 16 |

Rock (or ROCK) was a multithreading, multicore, SPARC microprocessor under development at Sun Microsystems. Now canceled, it was a separate project from the SPARC T-Series (CoolThreads/Niagara) family of processors.

Rock aimed at higher per-thread performance, higher floating-point performance, and greater SMP scalability than the Niagara family. The Rock processor targeted traditional high-end data-facing workloads, such as back-end database servers, as well as floating-point intensive high-performance computing workloads, whereas the Niagara family targets network-facing workloads such as web servers.

Processor core

The Rock processor implements the 64-bit SPARC V9 instruction set and the VIS 3.0 SIMD multimedia instruction set extension.[1] Each Rock processor has 16 cores, with each core capable of running two threads simultaneously, yielding 32 threads per chip. Servers built with Rock use FB-DIMMs to increase reliability, speed and density of memory systems. The Rock processor uses a 65 nm manufacturing process for a design frequency of 2.3 GHz.[2] The maximum power consumption of the Rock processor chip is approximately 250 W.[3]

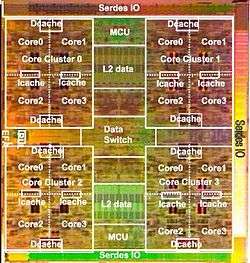

Core cluster

The 16 cores in Rock are arranged in four core clusters. The cores in a cluster share a 32 KB instruction cache, two 32 KB data caches, and two floating point units. Sun designed the chip this way because server workloads usually have high re-utilization in data and instruction across processes and threads but low number of floating-point operations in general. Thus sharing hardware resources among the four cores in a cluster leads to significant savings in area and power but low impact to performance.[4]

Unconventional features

In 2005, Sun publicly disclosed a feature in the Rock processor called hardware scout. Hardware scout uses otherwise idle chip execution resources to perform prefetching during cache misses.[5]

In March 2006, Marc Tremblay, Vice President and Chief Architect for Sun's Scalable Systems Group, gave a presentation at the Xerox Palo Alto Research Center (PARC) on thread-level parallelism, hardware scouting, and thread-level speculation.[6] These multithreading technologies were expected to be included in the Rock processor.

In August 2007, Sun confirmed that Rock would be the first production processor to support transactional memory.[7] To provide the functionality, two new instructions were introduced (chkpt, commit) with one new status register (cps). The instruction chkpt <fail_pc> is used to begin a transaction and commit to commit the transaction. If transaction abort condition is detected, jump to <fail_pc> is issued and cps can be used to determine the reason. The support is best-effort based, as in addition to data conflicts, transactions can be aborted by other reasons. These include TLB misses, interrupts, certain commonly used function call sequences and "difficult" instructions (e.g., division).[8] Nevertheless, many (arguably fine-grained) code blocks requiring synchronization could have benefited from transactional memory support of the Rock processor.[9]

In February 2008, Marc Tremblay announced a unique feature called "out-of-order retirement" at the ISSCC. The benefits include replacing the "traditional instruction window with this much smaller deferred queue".[10]

In April 2008, Sun engineers presented the transactional memory interface at Transact 2008, and the Adaptive Transactional Memory Test Platform simulator was announced to be made available to the general public shortly after.[8][11]

Server platforms

The Rock processor was intended to be used in Sun's proposed Supernova server line. Details of the server specifications were released in OpenSolaris Architecture Review case FWARC/2008/761.[12]

Physical resources

The Physical Resource Inventory (PRI) specification of ARC 2008/761 indicates the Supernova platforms would support: IEEE 1275 OpenFirmware, platform virtualization through Logical Domains (LDOMs), independent system controller (SC), and Fault Management Architecture (FMA) Domain Services.[13] The FMA feature was originally referenced to FWARC/2006/141, but this was closed and extended in FWARC/2008/455 "to successfully diagnose PCI fabric errors that occur in root domains."[14]

Input/output description

The iodevice Machine Description (MD) Node Specification of ARC 2008/761 indicates support for both PCI Express (PCIe) hot-pluggable slots as well as a bridge to older PCI eXtended (PCI-X)).[15]

Input/output expandability

Hitendra Zhangada, in the SPS Common Software Features Engineering group, at Sun described a variety of PCIe parameters in software which support the hardware platforms. "Bronze" servers would support PCIe slots 0-5. "Silver" servers would support I/O boards 0-1 and PCIe slots 0-7 for each board. "Platinum" servers would support I/O boards 0-3 and PCIe slots 0-7 for each board. "Silver-II" servers would support PCIe slots 00-19. "Platinum-II" servers would support boards 0-7 and slots 0-3 for each board.[16]

Common features

Zhangada sponsored a fast-track software ARC case describing Supernova platforms AT480 and AT880. Ravi Subbarao, Director of Enterprise Systems Software at Sun, sponsored ARC 2008/761, describing platforms bindings and interface changes for MD, PRI and OpenBoot devices.[16]

AT7180

The SPARC Enterprise AT7180 was speculated to be a single socket model handling as many as 32 hardware threads.[17]

AT7280

The SPARC Enterprise AT7280 was speculated to be a dual socket model handling as many as 64 hardware threads.[18]

AT7480

The Supernova Silver-II was proposed to be named the SPARC Enterprise AT7480, a quad socket model reported to handle as many as 128 hardware threads,[19] based on the PCI Express bus architecture with Open Boot firmware.

AT7880

The Supernova Platinum-II was proposed to be named the SPARC Enterprise AT7880, an eight-socket model reported to handle as many as 256 hardware threads,[20] based on the PCI Express bus architecture with Open Boot firmware. Pingchung Lee explained in a December 10, 2008 email for ARC case 2008/761 that the AT7880 would have eight individual CPU boards, each with one Sun Neptune multithreaded 10 Gigabit Ethernet chip.[21]

Product history

In February 2005, the CEO of Sun Microsystems, Scott McNealy, stated that the "taping out" of Rock would be on schedule later that year.[22] However, this tape-out was ultimately delayed to January 2007.[23]

In April 2007, Sun CEO Jonathan I. Schwartz blogged an image of a BGA-packaged Rock chip, labeled UltraSPARC RK, and disclosed that it could address 256 terabytes of virtual memory in a single system running Solaris.[24] The next month, Sun announced that they had created a Rock chip that could boot its operating system, Solaris, successfully.[25] In August of the same year, Sun released details on the use of transactional memory in the Rock architecture.[26] However, as a result of "entirely new design and given its uniqueness and complexity", the release of Rock was delayed to 2008 or 2009.[27]

In 2008, Mark Moir presented "Rock's Transactional Memory and How to Exploit It" at Sun Labs Open House 2008, discussing transactional memory as well as scouting threads and how these mitigated the computing problems not solved by innovative use of massive thread counts of slower processors.[28] That September, the OpenSolaris project began to integrate code supporting the Rock-based SuperNova program.[29]

In January 2009, Sun CEO Jonathan Schwartz announced Rock was still on track for a 2009 release.[30] On 10 March 2009 Dave Dice, Yossi Lev, Mark Moir and Dan Nussbaum presented "Early Experience with a Commercial Hardware Transactional Memory Implementation" at the Fourteenth International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS '09). They published their "experience with the hardware transactional memory (HTM) feature of two pre-production revisions of a new commercial multicore processor" in 2009.[31][32][33]

Cancellation

On April 20, 2009, Sun and Oracle Corporation announced that they had entered into a definitive agreement under which Oracle would acquire Sun. A June 12 posting on a Sun blog announced a technical NDA-only presentation on ROCK on July 14, 2009 at the Hamburg OpenSolaris Users Group Meeting.[34]

On 15 June 2009, the New York Times reported that "two people briefed on Sun’s plans" said the Rock project was canceled. Sun did not comment.[35][36] Two days later, the EE Times reported that "Sun did not submit a paper on Rock [to Hot Chips 21] leading to speculation the company may have canceled the chip."[37] On 24 June 2009, a presentation on "Speculative Threading & Parallelization" featured "A Novel Pipeline Architecture Implemented in Sun's ROCK Processor" at The 36th International Symposium on Computer Architecture.[38]

On 6 August 2009, support for Rock was removed from the OpenSolaris Project.[39] On 13 August 2009, a presentation on "NZTM: Nonblocking Zero-indirection Transactional Memory" written by Fuad Tabba, Mark Moir, James Goodman, Andrew Hay, and Cong Wang, was presented at the 21st ACM Symposium on Parallelism in Algorithms and Architectures in Calgary, Canada. The NZSTM algorithm performance was evaluated on Sun’s forthcoming Rock processor.[40][41] On 11 September 2009, The Register reported that the Rock processor was left out of the SPARC processor roadmap then being shown to Sun's customers and partners.[42] On 15 September 2009, the paper tm_db: A Generic Debugging Library for Transactional Programs, written by Yossi Lev and Maurice Herlihy, was presented at The Eighteenth International Conference on Parallel Architectures and Compilation Techniques (PACT) Raleigh, North Carolina.[43][44]

On 26 October 2009, Dave Dice, Yossi Lev, Mark Moir and Dan Nussbaum expanded a formerly published paper "Early Experience with a Commercial Hardware Transactional Memory Implementation" which was presented at the Fourteenth International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS '09).[45]

On January 27, 2010, Oracle announced it had completed its acquisition of Sun. On 5 April 2010, Dave Dice, Yossi Lev, Virendra Marathe, Mark Moir, Marek Olszewski and Dan Nussbaum released a paper "Simplifying Concurrent Algorithms by Exploiting Hardware Transactional Memory" to be presented at the 22nd ACM Symposium on Parallelism in Algorithms and Architectures (SPAA 2010).[46][47]

On 5 April 2010, Dave Dice and Nir Shavit released a paper "TLRW: Return of the Read-Write Lock" to be presented at SPAA 2010.[46][48] On 12 May 2010, Reuters reported that Oracle CEO Larry Ellison shut down the Rock project when Oracle acquired Sun, quoting him as saying, "This processor had two incredible virtues: It was incredibly slow and it consumed vast amounts of energy. It was so hot that they had to put about 12 inches of cooling fans on top of it to cool the processor. It was just madness to continue that project."[49]

References

- ↑ Liang He; Harlan McGhan (May 2005). "MT mediaLib for Chip MultiThreaded (CMT) Processors" (PDF). Sun Microsystems, Inc. Retrieved 2007-12-03.

- ↑ Neal, Brian (March 24, 2003). "Architecting the Future: Dr. Marc Tremblay". Ace's Hardware.

- ↑ "Rock: A SPARC CMT Processor" (PDF). Sun Microsystems. 2008-08-26.

- ↑ "A Third-Generation 65nm 16-Core 32-Thread Plus 32-Scout-Thread CMT SPARC(R) Processor" (PDF). Sun Microsystems. 2008-02-13.

- ↑ Chaudhry, S.; Yip, S.; Caprioli, P; Tremblay, Marc (2005). "High Performance Throughput Computing". IEEE Micro. 25 (3): 32. doi:10.1109/MM.2005.49.

- ↑ Tremblay, M. (March 2, 2006). "High Performance Throughput Computing". PARC Forum. Palo Alto, CA.

- ↑ "Transactional Memory". Sun Microsystems. 2007-08-13.

- 1 2 Moir, Mark; Moore, Kevin; Nussbaum, Dan (2008-02-22). "The Adaptive Transactional Memory Test Platform: A Tool for Experimenting with Transactional Code for Rock" (PDF). TRANSACT 2008. Retrieved 2009-02-20.

- ↑ "Applications of the Adaptive Transactional Memory Test Platform" (PDF). Sun Microsystems. 2008-02-13.

- ↑ "Sun: Can you smell what the Rock is cookin'?". Arstechnica. 2008-02-04.

- ↑ "Rock's Transactional Memory". Sun Microsystems. 2008-04-25.

- ↑ "Open Solaris: What is an ARC Review?". OpenSolaris.org."FWARC/2008/761". OpenSolaris.org.

- ↑ "PRI Specification 1.6". acclinet. 2008-12-15.

- ↑ "FMA IO Domain Service". OpenSolaris.org. 2008-07-17.

- ↑ "iodevice MD Node Specification". OpenSolaris.org. 2008.

- 1 2 "fast-track : 2008/761 - Supernova Platform Binding". OpenSolaris.org. 2008-12-09.

- ↑ "Sun Servers Sun AT7180". acclinet.

- ↑ "Sun Servers Sun AT7280". acclinet.

- ↑ "Sun Servers Sun AT7480". acclinet.

- ↑ "Sun Servers Sun AT7880". acclinet.

- ↑ "Sun Servers Sun AT7880". acclinet.

- ↑ "Sun burnishes next-gen Sparc chips". cnet. 2005-05-03.

- ↑ "Sun Expands Solaris/SPARC CMT Innovation Leadership". Sun Microsystems. 2007-01-18.

- ↑ "Rock Arrived". Sun Microsystems. 2007-04-10.

- ↑ "Sun Microelectronics Hits Key Milestone in High-End UltraSPARC Development". Sun Microsystems. 2007-05-02.

- ↑ "Sun slots transactional memory into Rock". The Register. 2007-08-21.

- ↑ "Sun's Rock chip waves goodbye to 2008 ship date; Shaky silicon eyes 2009". The Register. 2007-12-27.

- ↑ "Mark Moir presents at Sun Labs Open House 2008:Rock's Transactional Memory and How to Exploit It". Sun.

- ↑ "Heads-up: Solaris support for Rock processor". OpenSolaris Project. Archived from the original on 2008-10-02.

- ↑ "Sun will Rock in 2009:UltraSparc hope". The Register.

- ↑ "ASPLOS 2009 program". 2009-03-10.

- ↑ "Early Experience with a Commercial Hardware Transactional Memory Implementation" (PDF). March 2009.

- ↑ "Early Experience with a Commercial Hardware Transactional Memory Implementation (slides)" (PDF). March 2009.

- ↑ "pre-HHOSUG: ROCK NDA gift..". 2009-06-12.

- ↑ Vance, Ashlee (2009-06-15). "Sun Is Said to Cancel Big Chip Project". The New York Times. Retrieved 2010-05-22.

- ↑ "Sun's Rock Doomed from the Start, Analysts Say". PC World. 2009-06-18.

- ↑ "CPUs gear up for--and some avoid--Hot Chips". EETimes. 2009-06-17.

- ↑ "The 36th International Symposium on Computer Architecture". 2009-06-20.

- ↑ "6858457 Remove Solaris support for UltraSPARC-AT10 processor". 2009-08-09.

- ↑ "NZTM: Nonblocking Zero-indirection Transactional Memory" (PDF). September 2009.

- ↑ "SPAA 2009 Program" (PDF). 2009-08-13.

- ↑ "Sun's Sparc server roadmap revealed". The Register. 2009-09-11.

- ↑ "tm_db: A Generic Debugging Library for Transactional Programs". 2009-09-15.

- ↑ "tm_db: A Generic Debugging Library for Transactional Programs" (PDF). 2009-09-15.

- ↑ "Early Experience with a Commercial Hardware Transactional Memory Implementation". 2009-10-26.

- 1 2 "SPAA 2010 Conference Program". 2010.

- ↑ "Simplifying Concurrent Algorithms by Exploiting Hardware Transactional Memory". 2010-04-05.

- ↑ "LRW: Return of the Read-Write Lock". 2010-04-05.

- ↑ "Special Report: Can that guy in Ironman 2 whip IBM in real life?". Reuters. 2010-05-12.

Further reading

- "Sun's Rock CPU Could Be a Gem for Oracle". IEEE Spectrum. 2009-06-01.