microSPARC

| Produced | From 1992 to 1994 |

|---|---|

| Designed by | Sun Microsystems |

| Max. CPU clock rate | 40 MHz to 125 MHz |

| Instruction set | SPARC V8 |

| Cores | 1 |

The microSPARC (code-named "Tsunami") is a microprocessor implementing the SPARC V8 instruction set architecture (ISA) developed by Sun Microsystems. It was a low-end microprocessor intended for low-end workstations and embedded systems. The microprocessor was developed by Sun, but the floating-point unit (FPU) was licensed from Meiko Scientific. It contained 800,000 transistors.

There were two derivatives of the microSPARC: the microSPARC-II and microSPARC-IIep. The microSPARC-IIep was a 100 MHz microSPARC-II with an integrated PCI controller for embedded systems. It was developed and fabricated by LSI Logic for Sun. The microprocessor was used by Sun in their JavaStation Network Computer.

| Name (codename) | Model | Frequency (MHz) | Arch. version | Year | Total threads[1] | Process (µm) | Transistors (millions) | Die size (mm²) | IO Pins | Power (W) | Voltage (V) | L1 Dcache (k) | L1 Icache (k) | L2 Cache (k) | L3 Cache (k) |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| microSPARC I (Tsunami) | TI TMS390S10 | 40–50 | V8 | 1992 | 1×1=1 | 0.8 | 0.8 | 225? | 288 | 2.5 | 5 | 2 | 4 | none | none |

| microSPARC II (Swift) | Fujitsu MB86904 / Sun STP1012 | 60–125 | V8 | 1994 | 1×1=1 | 0.5 | 2.3 | 233 | 321 | 5 | 3.3 | 8 | 16 | none | none |

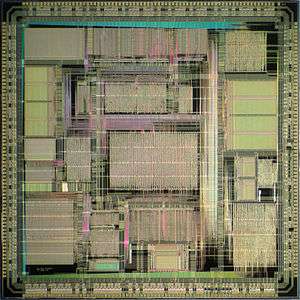

- Die photos

TI microSPARC I

TI microSPARC I- Sun microSPARC II

References

- ↑ Threads per core × number of cores

- Sun Microsystems, Inc. (10 August 1992). "Highly Integrated SPARC Processor Implementation (Tsunami)". Hot Chips presentation.'

This article is issued from Wikipedia - version of the 7/28/2016. The text is available under the Creative Commons Attribution/Share Alike but additional terms may apply for the media files.